芯片堆叠技术能否实实在在解决国产芯片难题?

发布时间:2022-12-26 08:35:30 浏览:418次 责任编辑:腾盛精密

芯片堆叠技术作为一个新的概念,其在近几年成为半导体领域研究热点,但这一技术是否能够为国产芯片发展带来实质性的改变呢?

华为芯片堆叠技术之路

众所周知,CPU是一个超大规模的集成电路板,指甲盖儿大小的芯片上安置着数以亿计的晶体管,再也留不出任何空白的地方,那为何不再叠加一张纸放在它的上面呢?3D堆叠由此产生。

所谓的3D堆叠技术其实很好理解,就是在原本的封装体里面,封装进两个以上不同功能的芯片,一般都是在不改变原本的封装体积大小,而在垂直方向进行的芯片叠放。

这种技术所带来的特点就是改变了原有的在单位面积上不断增加晶体管的方式,而是在垂直方向上进行芯片叠放,自然也会实现芯片的功能多样化。

早在2012年,华为便已经对芯片堆叠技术进行专利公开,该专利为“芯片堆叠封装结构”(申请公布号:CN102693968A),主要设计芯片封装技术领域,实现芯片的高密度堆叠,提高芯片堆叠封装结构的散热效率。

其后几年,华为也在不断对外公开其芯片堆叠的相关技术,足以证明长期以来华为都在这项技术上深耕研发。

比如近几年,华为所公布的两项芯片堆叠相关专利,一项是“一种多芯片堆叠封装及制作方法”(申请公布号:CN114287057A),解决因采用硅通孔技术而导致的成本高的问题。

另一项为“芯片堆叠封装结构及其封装方法、电子设备”(申请公布号:CN114450786A),用于解决如何将多个副芯片堆叠单元可靠的键合在同一主芯片堆叠单元上的问题。

▲华为专利 (来源:国家知识产权官网)

其实说到底,堆叠芯片就是利用先进的封装技术去绕开EUV的“紧固”,放出高性能的芯片。多项与芯片堆叠相关专利的公开,或许也揭露了华为未来在芯片技术上的一个发展方向。

目前,3D芯片技术的类别包括:基于芯片堆叠的3D技术,基于有源TSV的3D技术,基于无源TSV的3D技术,以及基于芯片制造的3D技术。

3D堆叠应用商业化普及

苹果此前已经向我们证明,芯片堆叠技术是可以大幅提升处理器的性能的。前不久发布的M1 Ultra芯片,就是通过两块M1 Max芯片封装而来的。

M1 Ultra将两枚M1 Max中隐藏的芯片间互连模块(die-to-die connector)通过技术手段整合在一起,苹果将其称之为“Ultra Fusion”架构,拥有1万多个信号点,互连带宽高达2.5TB/s,而且延迟、功耗都非常低。

这种堆叠方式可在性能、能耗和功能上带来各种意想不到的好处。

没有这种技术,苹果智能手表Apple Watch也就无法做出来,三星最先进的固态存储器、来自英伟达和谷歌的人工智能系统和索尼超级快速的新型相机也不例外。

芯片堆叠也带来了一些全新的功能。有的手机摄像头将图像传感器直接叠加在处理图像的芯片上面。额外的速度意味着,它们能够对照片进行多次曝光,并将其融合在一起,在昏暗的场景里捕捉到更多的光线。

3D堆叠式芯片的普及非常快速,它们也必然会成为行业主流。10年前,该技术几乎仅仅存在于高校实验室;五六年前,还难以找到它的商业化案例。但它如今如雨后春笋般涌现,出现在各类的应用上,如网络化、高性能计算和Apple Watch等高端可穿戴设备。

芯片堆叠关键工艺及局限性

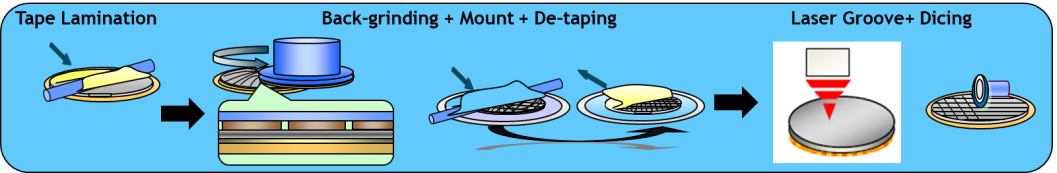

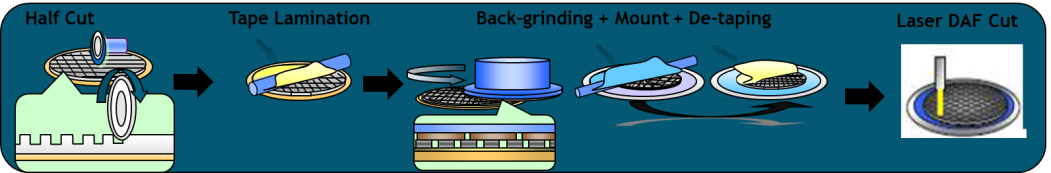

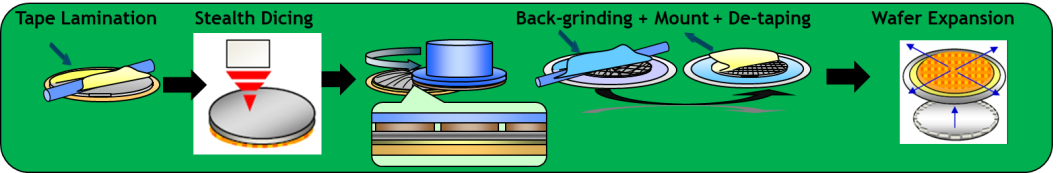

▲SDBG(来源:DISCO)

芯片堆叠技术推动国产芯片量产

在诸多限制和封锁下,我国一直缺乏半导体关键设备EUV光刻机,这就导致中国在推进7nm工艺乃至更先进的工艺方面始终无法突破,但是中国芯片行业采取了两条路线齐步走的方式发展芯片。

其中一条路线就是积极推进国产芯片制造产业链的完善和技术升级;另一条路线则是研发先进的封装技术,例如华为芯片堆叠技术将两枚同样以14nm工艺生产的芯片堆叠在一起,从而取得接近7nm工艺的性能。

▲Kirin芯片(来源:网络)

堆叠技术并非新技术,华为此项专利只是其中一个堆叠方法的专利展示。至少为国内被芯片“卡脖子”提出了解决方案之一,在此研发过程所沉淀和积累下来的研发能力、研发队伍、研发平台也是有价值的。

Tensun腾盛作为在半导体封测领域有着十六年经验的精密装备供应商,也一直不断探索SiP先进封装领域产品设备的开发和制程应用,致力于为客户提出半导体制程封测的解决方案。

只要有市场,中国芯片就能引领世界,芯片堆叠技术能最大化发挥目前的国产芯片资源优势。5G技术融入到各行各业,帮助传统企业快速转型升级,利用我们自身的优势去提高行业发展。

————

声明:本文部分内容参考出处有:

1.「华为公布芯片新专利,堆叠封装的利与弊各是什么?」,来源:物联网智库

2.「华为首次公开芯片堆叠封装技术!」,来源:云脑智库

3.「一文解析多芯片堆叠封装技术」,来源:电子发烧友

如有侵权等行为,可联系我方删除。

深圳市腾盛精密装备股份有限公司

深圳市腾盛精密装备股份有限公司